"무어의 법칙은 반도체 업계를 이끄는 원동력이며 인텔이 성능 향상을 위해 트랜지스터 당 비용 절감을 지속 추진하는 이유이기도 하다. 인텔 엔지니어들은 수년 동안 무어의 법칙을 달성하기 위해 다양한 옵션과 기술을 추구해 왔다."

18일 오전 온라인으로 진행된 패키징 기술 브리핑에서 톰 러커 인텔 어셈블리·테스트 부문장(부사장)이 이같이 설명했다.

인텔은 이날 3D 반도체 적층 기술인 포베로스를 올 하반기 출시할 첫 타일 구조 코어 프로세서, '메테오레이크'(Meteor Lake)부터 본격 적용할 것이라고 설명했다. 또 반도체를 부착하는 기판을 2020년대 말까지 유리 석영 재질로 교체할 것이라고 밝혔다.

■ 1965년 등장 '무어의 법칙', 최근 10여년 간 정체

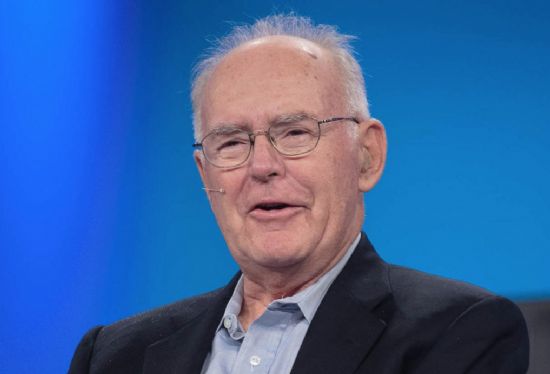

'무어의 법칙'은 지난 3월 말 별세한 인텔 창업자, 고든 무어가 1965년 학술지 '일렉트로닉스'에 기고한 논문에서 출발했다. 당시 그는 "최소한의 비용 상승으로 칩에 들어가는 트랜지스터 수가 2년마다 2배씩 늘어나며 성능도 향상될 것"이라고 예측했다.

무어의 법칙은 이후 미세 공정 개발, 새로운 트랜지스터 구조 적용 등으로 2010년 경까지 지속 유지되었다. 그러나 현재는 트랜지스터 수를 늘릴 수 있는 가장 효율적인 수단인 공정 미세화 등에서 정체 현상이 지속되고 있다.

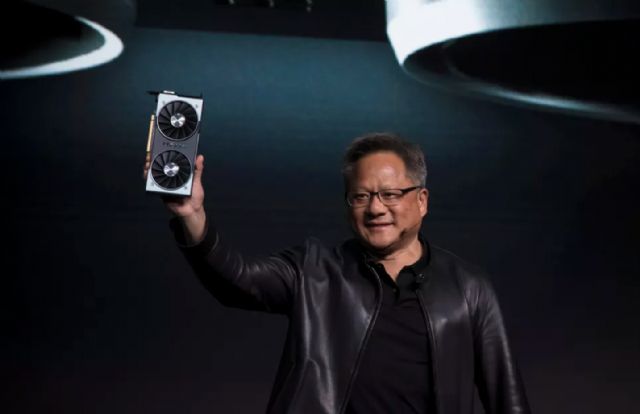

젠슨 황 엔비디아 CEO는 CES 2019 기조연설에서 "무어의 법칙은 죽었다"고 선언하기도 했다 반도체 설계 IP 전문 기업인 ARM은 2021년 "무어의 법칙 대신 반도체의 효율성을 따지는 '와트 당 성능'이 새로운 기준이 되어야 한다"고 주장했다.

■ "고든 무어, 기능 별 반도체 생산·패키징 기술에 선견지명"

'무어의 법칙'에서는 트랜지스터 수 증가와 성능 증가만 주목받는 경향이 있다. 그러나 당시 고든 무어는 "대규모 시스템을 작은 기능별로 나눈 다음 서로 연결하는 것이 더 경제적이라는 사실이 증명될 것"이라고 예측하기도 했다.

톰 러커 인텔 어셈블리·테스트 부문장(부사장)은 18일 "고든 무어는 생산된 반도체를 다른 부품과 연결하고 작동할 수 있도록 처리하는 '패키징' 공정에도 일종의 선견지명을 가지고 있었다"고 설명했다.

톰 러커 부문장은 "패키징 기술은 웨이퍼에 새겨진 반도체 다이(Die)를 PC나 서버 메인보드 등으로 이어주는 다리 역할을 한다. 처리할 데이터와 함께 반도체 생산 비용도 늘어나고 있으며 여러 반도체를 한 패키지 안에 넣는 보다 발전된 패키징 기술이 필요하다"고 설명했다.

■ 2019년 반도체 쌓는 '포베로스' 기술 개발

인텔은 2000년대 이후부터 서로 다른 반도체를 한데 묶는 패키징 기술을 지속 연구해 왔다. 양대 축을 이루는 기술 중 하나로 2019년 개발된 반도체 적층 기술, 포베로스(FOVEROS)가 있다.

포베로스가 처음 적용된 제품은 2020년 출시된 하이브리드 프로세서(개발명 레이크필드)다. 가로·세로 12×12mm 공간에 고성능 코어 1개, 저전력·고효율 코어 4개와 메모리를 쌓아올렸다.

톰 러커 부문장은 "하이브리드 프로세서는 논리 회로 위에 논리 회로를 쌓는 방식으로 개발되었고 가로·세로 면적에 제약이 있는 노트북용 고성능 프로세서를 개발했다는 데 의의가 있다"고 설명했다.

■ 하반기 출시될 '메테오레이크'에 2세대 포베로스 기술 적용

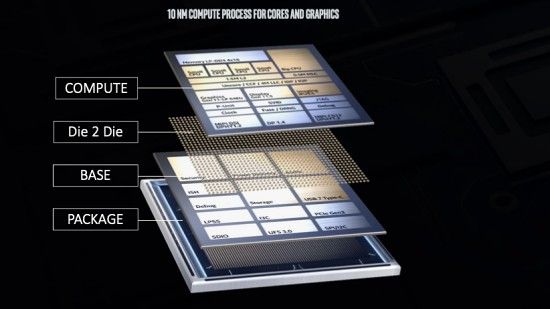

인텔이 올 하반기 출시할 차세대 코어 프로세서, 메테오레이크(Meteor Lake)는 인텔 적층형 기술인 포베로스(FOVEROS)를 바탕으로 CPU와 그래픽칩셋 등을 타일 형태로 쌓아올리는 방식으로 제조된다.

연산을 담당하는 CPU 타일은 EUV(극자외선)를 활용한 인텔 4 공정에서, 내장 그래픽칩셋은 대만 TSMC N5(5나노급) 공정에서 생산된다. 입출력을 담당하는 IOE 타일, SoC 타일 역시 인텔 외부에서 생산한다.

푸야 타다욘 인텔 펠로우는 "메테오레이크에 적용된 포베로스 기술은 반도체 사이 접점 간격을 36미크론(0.036mm)까지 줄인 2세대 기술이며 내년에는 접점 간격을 25미크론(0.025mm)까지 줄일 것"이라고 설명했다.

■ "데이터센터 GPU 맥스, 가장 앞선 패키징 기술 적용"

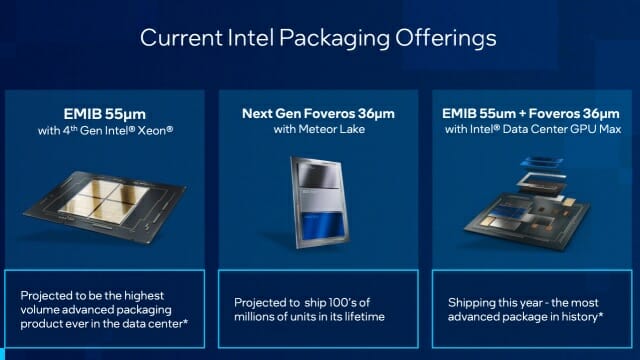

지난 1월 정식 출시된 4세대 제온 스케일러블 프로세서는 반도체 조각을 평면으로 배열하는 EMIB 기술을 이용해 최대 60코어를 구현했다. 올 4분기 출시 예정인 5세대 제온 스케일러블 프로세서(에메랄드래피즈) 역시 최대 2개 CPU 타일을 조합할 예정이다.

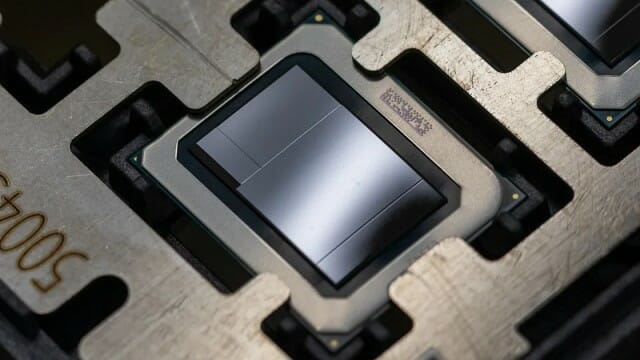

서버용 GPU인 데이터센터 GPU 맥스(폰테 베키오)는 EMIB과 포베로스 등 양대 첨단 패키징 기술을 모두 적용했다. Xe 그래픽코어 128개와 최대 128GB HBM2e, 408MB 람보 L2 캐시 등을 탑재한 가장 복잡한 프로세서 중 하나다.

푸야 타다욘 인텔 펠로우는 "포베로스가 적용된 메테오레이크는 향후 수 억 개 이상 시장에 공급될 예정이며 데이터센터 GPU 맥스는 현재 가장 앞선 패키징 기술을 적용했다"고 설명했다.

■ "유리 석영 기판·광신호 전달 기술 연구중"

관련기사

- 인텔, 2022-2023 연례 기업 책임 보고서 공개2023.05.15

- 인텔 팻 겔싱어 "메테오레이크 웨이퍼 양산 돌입"2023.04.28

- 인텔 공동 창업자 고든 무어 별세…'무어의 법칙' 창시2023.03.26

- 강문수 부사장 "비욘드 무어 시대…첨단 패키지 기술이 주도"2023.03.23

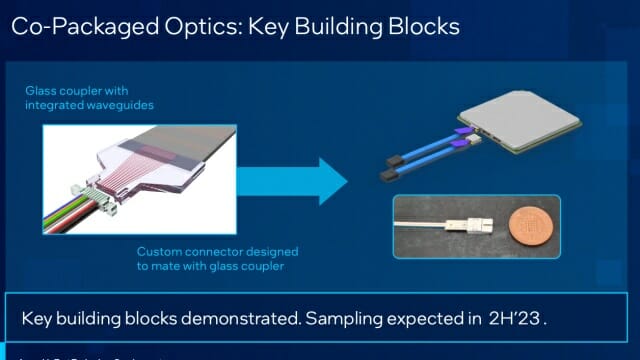

인텔은 이날 "반도체를 부착하는 기판을 2030년 말까지 유리 석영 재질로 바꿀 것"이라고 밝혔다. 푸야 타다욘 펠로우는 "유리 석영 기판은 전력 소모 등을 줄일 수 있는 장점이 있다"고 설명했다.

이어 "반도체 신호 전송을 전기 신호에서 광섬유를 이용하는 방식으로 전환하고 프로세서나 반도체에 직접 광신호를 전달할 수 있는 유리 기반 커플러를 개발중이며 올 하반기에 시제품이 나올 것"이라고 설명했다.